| 【DMA】如何保证 DMA 和 cache 的一致性 | 您所在的位置:网站首页 › STM32H7解决DMA伪双缓存中的出现Cache问题 › 【DMA】如何保证 DMA 和 cache 的一致性 |

【DMA】如何保证 DMA 和 cache 的一致性

|

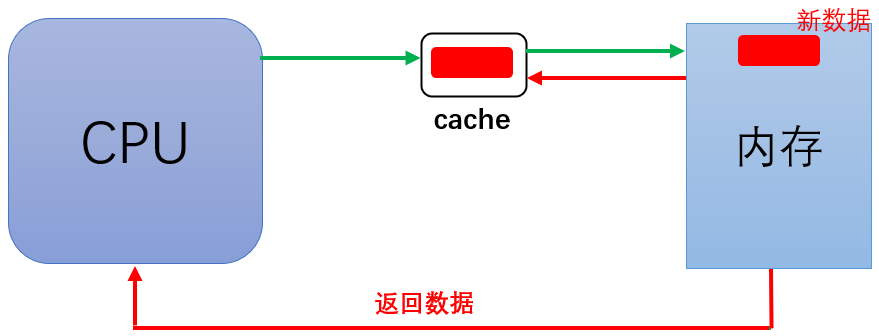

一方面,当 CPU 要从cache 读取数据时,会先检查cache是否命中,如果命中就直接返回,此时便不再访问内存;另一方面,DMA 在 向内存写入数据。这样一来就造成了DMA 传输的内容和cache中缓存的内容不一致。

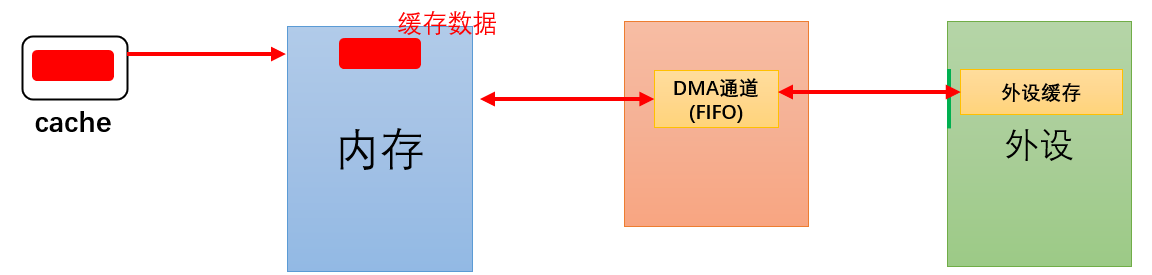

DMA 向内存写入数据 当 CPU 收到 DMA 的写请求时,说明有新数据要来了,为了保证一致性,CPU 要先清空 cache 先对 cache 进行 clean 操作(检查dirty位,如果为真,写回下一级存储)再进行 invalid 操作,让 cache 中的数据无效化,下一次访问 cache,直接访问内存

当内存中有新数据时,因为缓冲策略,一方面会将数据返回给CPU,另一方面也会在cache中保存一份新数据。

DMA 从内存读取数据 当 CPU 收到 DMA 的读请求时,说明DMA要将数据写入到外设了,此时CPU 需要对 cache 进行flush 操作,将数据刷到内存中,此时 DMA 读取到的就是最新的数据了。

参考文章: DMA cache一致性怎么保持(修改中)_星空语的博客-CSDN博客 内存CACHE中invaild、clean、flush的作用_cache flush_秋绘の枫的博客-CSDN博客 |

【本文地址】

公司简介

联系我们